# Evaluation of State-of-the-Art Hardware Architectures for Fast Cone-Beam CT Reconstruction

Der Technischen Fakultät der Universität Erlangen-Nürnberg

zur Erlangung des Grades

# DOKTOR-INGENIEUR

vorgelegt von

Holger Scherl

Erlangen — 2010

# Deutscher Titel: Evaluation moderner Hardwarearchitekturen zur schnellen CT Rekonstruktion aus Kegelstrahlprojektionen

Als Dissertation genehmigt von der Technischen Fakultät der Universität Erlangen-Nürnberg

Tag der Einreichung: 26.04.2010 Tag der Promotion: 19.10.2010

Dekan: Prof. Dr.-Ing. R. German Berichterstatter: Prof. Dr.-Ing. J. Hornegger

Prof. Dr. A. Bode

# Foreword by Professor Joachim Hornegger

Computed tomography is no longer limited to diagnostic imaging procedures but is nowadays routinely used in interventional radiology. The key requirement of interventional radiologists is a reconstruction time of less than 30 seconds. The usage of hardware accelerators and the development of highly optimized reconstruction algorithms is therefore not an option but mandatory from a practitioner's point of view. Especially the extension of C-arm devices with 3-D imaging capabilities has increased the demands on fast and efficient 3-D reconstruction machines. The assessment of the wide range of modern hardware accelerators for computed tomography is an emerging field. Many research teams work world wide on this problem. The large number of scientific publications on hardware accelerated 3-D reconstruction demonstrates the strong activities in this field. Most of the research is accompanied by industry that has an enormous pressure to get access to low-cost and high performance solutions.

In this book Dr. Holger Scherl considers the field of computed tomography including a review of state-of-the-art reconstruction algorithms and a concise assessment of the most recent hardware architectures. The text introduces the reader to the reconstruction problem in computed tomography and its major scientific challenges that range from computational efficiency to the fulfillment of Tuy's sufficiency condition. The assessed hardware architectures include multi- and many core systems, cell broad-band engine architecture, graphics processing units (GPUs), and field programmable gate arrays. The focus of this book is on the interplay of these recent hardware platforms and modern computed tomography reconstruction algorithms.

Dr. Scherl developed and evaluated a hard- and software framework that is unique and serves as a base for several research projects that deal with hardware accelerated reconstruction. Today the developed system is also used within product implementations in industry, and this particular transfer of the software platform from research to industry is exceptional. The pioneering work is not only appreciated by industry but also by the research community. Holger Scherl's initial publication on the GPU implementation of the reconstruction pipeline using CUDA is referenced more than 50 times.

I consider this book to be unique both in the degree of detail in the experimental evaluation and in the algorithms used for assessment. To my knowledge Holger Scherl is the first researcher considering both modern hardware architectures and most recent computed tomography algorithms.

I am pretty much convinced that the reader of this book will experience many novel aspects of computed tomography algorithms and their implementation on different hardware architectures.

Erlangen, 2011-04-04

Prof. Dr.-Ing. Joachim Hornegger

# Acknowledgments

I would like to thank my advisor Prof. Dr. Joachim Hornegger (LME, University of Erlangen-Nuremberg) for introducing me to the challenging research area of medical imaging and image reconstruction in computed tomography. Thank you for your support during my time as a graduate student in your research group. I am deeply grateful for your friendly assistance and your constant encourougement to all concerns about research related issues and private matters! I also wish to thank Prof. Dr. Arndt Bode (LRR, TU Munich) for reviewing this thesis.

I wish to give very special thanks to Dr. Markus Kowarschik (Siemens Healthcare) for his guidance and motivating influence on my work. I have enjoyed our numerous and valuable scientific discussions throughout the years. He further did a great job in proofreading all parts of this thesis.

Furthermore, I would like to thank all my current and former colleagues and friends of the LME team. I would like to express my gratitude to Dr. Stefan Hoppe, Benjamin Keck (LME, University of Erlangen), Hannes Hofmann (LME, University of Erlangen) and Dr. Marcus Prümmer (LME, University of Erlangen) for the friendly and productive collaboration. Thank you very much for your cooperativeness which I have deeply appreciated!

In particular, I would like to strongly emphasize and to express my gratitude to all the students with whom I had the pleasure to collaborate over the last few years: Mario Körner, Hannes Hofmann, Mikulas Kovac, Rüdiger Bock, Sebastian Sauer, Rainer Grimmer and Gunnar Payer contributed many important pieces to my research that has finally led to the writing of this thesis.

I am further indebted to Dr. Wieland Eckert (Siemens Healthcare) for the great opportunity to contribute to the evaluation of the Cell processor. Moreover, I owe thanks to Dr. Günter Lauritsch (Siemens Healthcare) and Dr. Holger Kunze (Siemens Healthcare) for their constant willingness to discuss complex issues in the field of computed tomography. I also owe thanks to Dr. Klaus Engel for rendering the images of the reconstructed volume datasets, which are presented in the Appendix.

Finally, I would like to thank the Siemens AG for providing financial support for my research.

Last not least, I express my deep gratitude to my wife Claudia. Thanks for your patience and for your invaluable support!

Erlangen, 2010-04-26

Holger Scherl

## Abstract

We present an evaluation of state-of-the-art computer hardware architectures for implementing the FDK method, which solves the three-dimensional image reconstruction task in cone-beam computed tomography (CT). The computational complexity of the FDK method prohibits its use for many clinical applications unless appropriate hardware acceleration is employed. Today's most powerful hardware architectures for high-performance computing applications are based on standard multi-core processors, off-the-shelf graphics boards, the Cell Broadband Engine Architecture (CBEA), or customized accelerator platforms (e.g., FPGA-based computer components).

For each hardware platform under consideration, we describe a thoroughly optimized implementation of the most time-consuming parts of the FDK method; the filtering step as well as the subsequent back-projection step. We further explain the required code transformations to parallelize the algorithm for the respective target architecture. We compare both the implementation complexity and the resulting performance of all architectures under consideration using the same two medical datasets which have been acquired using a standard C-arm device. Our optimized back-projection implementations achieve at least a speed-up of 6.5 (CBEA), 22.0 (GPU), and 35.8 (FPGA) compared to a standard workstation equipped with a quad-core processor. It is demonstrated that three hardware platforms (namely CBEA, GPUs, and FPGA-based architectures) enable real-time CT reconstruction and therefore support highly efficient clinical workflow.

We further describe and evaluate an optimized CBEA-based implementation of the M-line method, which is a theoretically exact and stable reconstruction algorithm. The M-line method solves the problem of cone-artifacts, which may cover small object details, thus providing excellent image quality. Its implementation, however, has an increased computational complexity as the M-line method requires additional computations for the filtering of the projection images, e.g. derivative computation and filtering along oblique lines in the projections. The execution time of filtering increases by a factor of 3.5 compared to the FDK method. Nevertheless, we are able to demonstrate on-the-fly reconstruction capability on a dual Cell Blade.

Finally, we present an efficient implementation of the computationally most demanding steps in iterative reconstruction algorithms on off-the-shelf graphics boards. Because the back-projection step can be implemented similar to the FDK method we especially consider the forward-projection step. Our implementation is based on a ray casting algorithm in order to make efficient use of the texture hardware in current graphics accelerators. Using a reasonable parameter configuration the forward-projection step requires roughly twice as much processing time as the back-projection step.

X Abstract

# Kurzfassung

Wir präsentieren eine Evaluierung verschiedener moderner Computerarchitekturen zur Implementierung der FDK Methode, die das dreidimensionale Rekonstruktionsproblem in der Computertomographie aus Kegelstrahlprojektionen löst. Die Rechenkomplexität der FDK Methode verhindert deren Einsatz in vielen klinischen Applikationen, solange keine geeignete Hardwarebeschleunigung eingesetzt wird. Heutzutage basieren die meisten Hardwarearchitekturen, die für hochperformante Rechenanwendungen geeignet sind, auf gewöhnlichen Mehrkernprozessoren, auf der Cell Broadband Engine Architektur (CBEA), auf Standardgrafikbeschleunigerkarten oder auf maßgeschneiderten Beschleunigerarchitekturen wie beispielsweise FPGA-basierten Computerkomponenten. Wir beschreiben für jede betrachtete Hardwarearchitektur eine sorgfältig optimierte Implementierung der rechenaufwändigsten Schritte der FDK Methode: der Filterschritt sowie auch der darauffolgende Rückprojektionsschritt. Wir zeigen außerdem notwendige Codetransformationen um den Algorithmus für die einzelnen Zielarchitekturen zu parallelisieren. Wir vergleichen sowohl die Komplexität der Implementierungen als auch die erzielte Performanz aller betrachteter Architekturen anhand zweier medizinischer Datensätze, die mit einem C-Bogengerät aufgenommen wurden. Unsere optimierten Rückprojektionsimplementierungen erzielen im Vergleich zu einer Standard-Workstation mit einem Vierkernprozessor mindestens eine Beschleunigung um den Faktor 6.5 (CBEA), 22.0 (GPU) und 35.8 (FPGA). Es konnte gezeigt werden, dass drei Hardwareplattformen (CBEA, GPUs und FPGAbasierte Architekturen) eine CT-Rekonstruktion in Echtzeit ermöglichen und damit sehr effizient den klinischen Arbeitsablauf unterstützen.

Weiterhin beschreiben und evaluieren wir eine optimierte CBEA-basierte Implementierung der M-line Methode, die ein theoeretisch exaktes und stabiles Rekonstruktionsverfahren darstellt. Die M-line Methode liefert eine exzellente Bildqualität, da sie das Problem der Kegelstrahlartefakte, die kleine Objektdetails verdecken können, löst. Ihre Implementierung verlangt jedoch eine erhöhte Rechenkomplexität, weil die M-line Methode zusätzliche Berechnungen für die Filterung von Projektionsbildern erfordert, wie zum Beispiel die Berechnung von Ableitungen und die Filterung entlang schräger Linien innerhalb einer Projektion. Im Vergleich zur FDK Methode erhöht sich die Ausführungszeit der Filterung um den Faktor 3.5. Wir können dennoch auf einem dualen Cell Blade eine mit der Datenaufnahme schritthaltende Rekonstruktion erzielen.

Schließlich präsentieren wir eine effiziente Implementierung der rechenintensivsten Schritte eines iterativen Rekonstruktionsalgorithmus auf Standardgrafikbeschleunigern. Hierbei betrachten wir besonders den Vorwärtsprojektionsschritt. Die Implementierung des Rückprojektionsschrittes ist nahezu identisch mit deren Implemen-

xii Kurzfassung

tierung im Falle der FDK Methode. Um die Textureinheiten in aktuellen Grafikprozessoren effizient nutzen zu können, basiert unsere Implementierung auf einem sogenannten Strahlverfolgungsverfahren (ray casting). Unter Benutzung einer adäquaten Parameterkonfiguration benötigt der Vorwärtsprojektionsschritt ungefähr doppelt so viel Verarbeitungszeit wie der Rückprojektionsschritt.

# Contents

| 1 | Intr                                          | oducti                                              | ion        | 1                                                  |  |  |  |  |  |  |  |

|---|-----------------------------------------------|-----------------------------------------------------|------------|----------------------------------------------------|--|--|--|--|--|--|--|

|   | 1.1                                           | Reconstruction Algorithms                           |            |                                                    |  |  |  |  |  |  |  |

|   | 1.2                                           | Hardw                                               | vare Varia | ints                                               |  |  |  |  |  |  |  |

|   | 1.3                                           | Relate                                              | ed Work    |                                                    |  |  |  |  |  |  |  |

|   | 1.4                                           | Scope                                               | and Mair   | n Contribution of this Thesis                      |  |  |  |  |  |  |  |

|   | 1.5                                           | Outlin                                              | ıe         |                                                    |  |  |  |  |  |  |  |

| 2 | Algorithms for Cone-Beam Image Reconstruction |                                                     |            |                                                    |  |  |  |  |  |  |  |

|   | 2.1                                           | Prerec                                              | quisites . |                                                    |  |  |  |  |  |  |  |

|   | 2.2                                           | Algorithm                                           |            |                                                    |  |  |  |  |  |  |  |

|   |                                               | 2.2.1                                               | Algorith   | mic Steps                                          |  |  |  |  |  |  |  |

|   |                                               | 2.2.2                                               | Impleme    | entation Strategies                                |  |  |  |  |  |  |  |

|   |                                               |                                                     | 2.2.2.1    | Ramp Filtering                                     |  |  |  |  |  |  |  |

|   |                                               |                                                     | 2.2.2.2    | Back-Projection                                    |  |  |  |  |  |  |  |

|   |                                               | 2.2.3                                               | Complex    | xity Analysis                                      |  |  |  |  |  |  |  |

|   |                                               |                                                     | 2.2.3.1    | Filtering                                          |  |  |  |  |  |  |  |

|   |                                               |                                                     | 2.2.3.2    | Back-Projection                                    |  |  |  |  |  |  |  |

|   |                                               |                                                     | 2.2.3.3    | Comparison of Computation Times                    |  |  |  |  |  |  |  |

|   | 2.3                                           | 2.3 Selected Alternatives to the Feldkamp Algorithm |            |                                                    |  |  |  |  |  |  |  |

|   |                                               | 2.3.1                                               | The M-I    | Line Method                                        |  |  |  |  |  |  |  |

|   |                                               |                                                     | 2.3.1.1    | Algorithmic Steps                                  |  |  |  |  |  |  |  |

|   |                                               |                                                     | 2.3.1.2    | Implementation Strategies                          |  |  |  |  |  |  |  |

|   |                                               | 2.3.2                                               | Iterative  | e Reconstruction                                   |  |  |  |  |  |  |  |

|   |                                               |                                                     | 2.3.2.1    | Simultaneous Algebraic Reconstruction Technique 29 |  |  |  |  |  |  |  |

|   |                                               |                                                     | 2.3.2.2    | Implementation Strategies                          |  |  |  |  |  |  |  |

|   |                                               |                                                     | 2.3.2.3    | Other Iterative Algorithms                         |  |  |  |  |  |  |  |

|   | 2.4                                           | Summ                                                | ary        |                                                    |  |  |  |  |  |  |  |

| 3 | Des                                           | ign an                                              | ıd Imple   | ementation of a General Reconstruction Frame-      |  |  |  |  |  |  |  |

|   | wor                                           | $\mathbf{k}$                                        |            | 37                                                 |  |  |  |  |  |  |  |

|   | 3.1                                           | Motiva                                              | ation      |                                                    |  |  |  |  |  |  |  |

|   |                                               | 3.1.1                                               | Cone-Be    | eam CT Reconstruction                              |  |  |  |  |  |  |  |

|   |                                               | 3.1.2                                               | Target I   | Hardware Platforms                                 |  |  |  |  |  |  |  |

|   |                                               |                                                     | 3.1.2.1    | Multi-Core and Multi-Processor Systems 39          |  |  |  |  |  |  |  |

|   |                                               |                                                     | 3.1.2.2    | Cell Broadband Engine Architecture 40              |  |  |  |  |  |  |  |

|   |                                               |                                                     | 3.1.2.3    | Common Unified Device Architecture                 |  |  |  |  |  |  |  |

xiv

|   | 3.2         | Reconstruction System Design                            |

|---|-------------|---------------------------------------------------------|

|   |             | 3.2.1.1 Pipeline Design Pattern 41                      |

|   |             | 3.2.1.2 Concurrency                                     |

|   |             | 3.2.2 Parallelization Strategy                          |

|   |             | 3.2.2.1 Master/Worker Design Pattern                    |

|   |             | 3.2.2.2 Combination with the Pipeline Design Pattern 43 |

|   |             | 3.2.2.3 Hardware Abstraction                            |

|   |             | 3.2.3 Resource Management                               |

|   |             | 3.2.3.1 Processing Elements                             |

|   |             | 3.2.3.2 Data Buffers                                    |

|   | 3.3         | Implementation                                          |

|   |             | 3.3.1 Structure                                         |

|   |             | 3.3.2 Participants                                      |

|   |             | 3.3.3 Sample Code and Usage                             |

|   | 3.4         | Summary                                                 |

|   | <i>C</i> 11 |                                                         |

| 4 |             | Broadband Engine Architecture 53                        |

|   | 4.1         | Architecture                                            |

|   |             |                                                         |

|   |             | 4.1.2 The Synergistic Processor Elements                |

|   | 4.2         |                                                         |

|   | 4.2         | 1 0                                                     |

|   |             | 4.2.1 Filtering                                         |

|   |             | 4.2.2.1 Problem Partitioning                            |

|   |             | 4.2.2.2 Main Memory Access                              |

|   |             | 4.2.2.3 Code Optimization                               |

|   | 4.3         | Results                                                 |

|   | 1.0         | 4.3.1 Filtering                                         |

|   |             | 4.3.2 Back-Projection                                   |

|   | 4.4         | Summary                                                 |

|   |             |                                                         |

| 5 | Star        | ndard Multi-Core Processors 71                          |

|   | 5.1         | Architecture                                            |

|   | 5.2         | Feldkamp Algorithm                                      |

|   |             | 5.2.1 Filtering                                         |

|   |             | 5.2.2 Back-Projection                                   |

|   | 5.3         | Results                                                 |

|   | 5.4         | Summary                                                 |

| 6 | Gra         | phics Accelerator Boards 77                             |

| U | 6.1         | Architecture                                            |

|   | 6.2         | Feldkamp Algorithm                                      |

|   | 0.2         | 6.2.1 Filtering                                         |

|   |             | 6.2.2 Back-Projection                                   |

|   | 6.3         | Results                                                 |

| Contents | XV |

|----------|----|

|          |    |

|                    | 6.4                  | Summary                                                                                                                                                                                                                                                                                 | 86                                                             |  |  |

|--------------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|--|--|

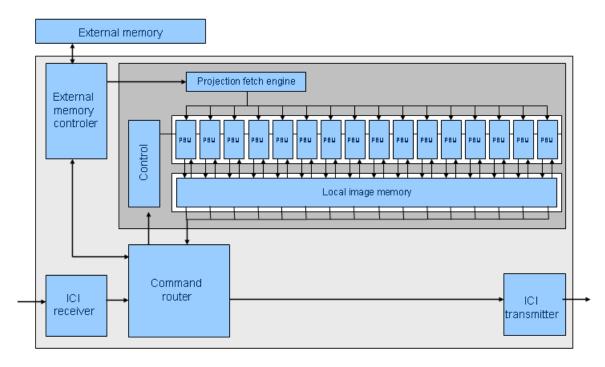

| 7                  | 7.1<br>7.2<br>7.3    | Architecture of the ImageProX Hardware Feldkamp Algorithm 7.2.1 Filtering 7.2.1.1 Block Floating-Point Mode 7.2.1.2 Unscaled Precision Mode 7.2.1.3 Implementation 7.2.2 Back-Projection Results 7.3.1 Simulation of Bit-Accurate Filtering 7.3.2 Filtering and Back-Projection Summary | 91<br>91<br>92<br>92<br>93<br>93<br>94<br>95<br>96<br>96<br>97 |  |  |

| 8                  | 8.1                  | formance Optimization of Selected Feldkamp Alternatives  M-line Method                                                                                                                                                                                                                  | 99<br>99<br>100<br>102                                         |  |  |

|                    | 8.2                  | Iterative Reconstruction                                                                                                                                                                                                                                                                | 104<br>104<br>108<br>110<br>114                                |  |  |

| 9                  | <b>Con</b> 9.1 9.2   | Summary                                                                                                                                                                                                                                                                                 | 115<br>115<br>118                                              |  |  |

| A                  | Geo                  | ometry Parameter Extraction                                                                                                                                                                                                                                                             | 121                                                            |  |  |

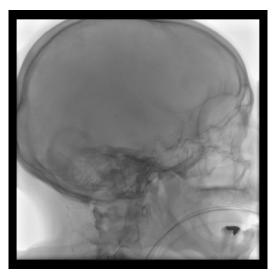

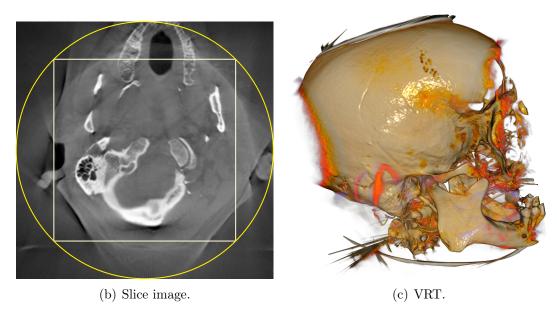

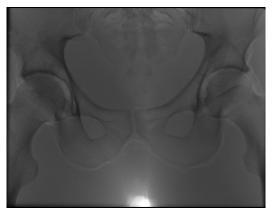

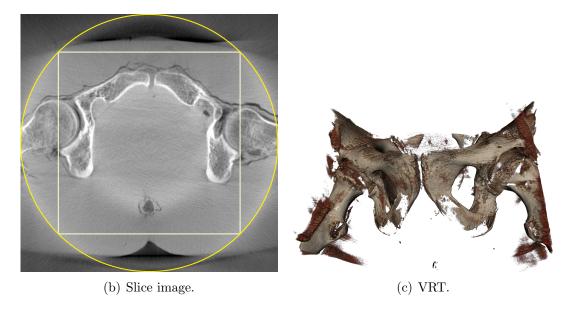

| В                  | <b>Dat</b> : B.1 B.2 | asets Dataset (a): Head                                                                                                                                                                                                                                                                 | 123<br>123<br>123                                              |  |  |

| $\mathbf{C}$       | Acre                 | onyms                                                                                                                                                                                                                                                                                   | 127                                                            |  |  |

| List of Figures    |                      |                                                                                                                                                                                                                                                                                         |                                                                |  |  |

| List of Tables     |                      |                                                                                                                                                                                                                                                                                         |                                                                |  |  |

| List of Algorithms |                      |                                                                                                                                                                                                                                                                                         |                                                                |  |  |

| Bibliography       |                      |                                                                                                                                                                                                                                                                                         |                                                                |  |  |

xvi

# Chapter 1

## Introduction

Computed tomography (CT) is a widely used imaging technique in the field of medical diagnosis and industrial non-destructive testing (NDT) applications. Using a sufficiently large series of X-ray images taken from different views around the object or patient a digital computer is used to generate slice images of the inside of the considered object or patient.

In modern CT devices three-dimensional (3-D) reconstruction techniques are employed that are able to deal with the cone-beam geometry resulting from X-ray projections that are measured with a two-dimensional detector array. This imaging approach enables the fast acquisition of the projection images and at the same time delivers high image quality. The computational complexity of the applied 3-D reconstruction methods prohibits their use in many medical applications without hardware acceleration. The use of hardware acceleration is therefore an important area of research in the field of cone-beam reconstruction. It is very important that advances in the theory of 3-D reconstruction go hand in hand with the development of suitable parallelization techniques that map them efficiently to appropriate hardware acceleration platforms.

## 1.1 Reconstruction Algorithms

A computationally efficient way to solve the reconstruction task is a technique which is called filtered back-projection (FBP). FBP methods achieve the reconstruction of an object by first filtering the cone-beam projections and then computing the back-projection of the filtered projections into the 3-D space.

The most successful full 3-D FBP algorithm was developed by Feldkamp, Davis, and Kress, which is commonly referred to as the FDK method [Feld 84]. The algorithm deals with a circular acquisition trajectory, where the X-ray source and the detector rotate around the center of the object to be scanned. It is equally possible to fix the X-ray source and detector while rotating the object, which is often the case in NDT applications.

The FDK method is used in most of today's cone-beam CT scanners such as C-arm devices, radiation therapy devices, dental CT devices, and in a modified way also in 3-D digital mammography devices and helical CT scanners (see Figure 1.1) as the standard image reconstruction approach.

(a) Helical CT scanner.

(b) Radiation therapy device.

(c) Robotic C-arm device.

(d) Mobile C-arm device.

(e) Ceiling-mounted C-arm device.

(f) Digital mammography device (3-D breast tomosynthesis).

Figure 1.1: Several medical devices using CT imaging. By courtesy of Siemens AG.

In medical imaging a high image quality is required. Using the state-of-the-art FDK method, however, the occurring cone artifacts may cover small object details complicating their distinction. Cone artifacts manifest in the reconstruction as blurred zones at high density contrasts in the direction of the rotation axis. In medical datasets high density contrasts are located mainly at the transition between bone structures and tissue or air. The approximative nature of the Feldkamp algorithm is due to two reasons. First, the circular acquisition does not fulfill the data completeness condition necessary to compute a 3-D reconstruction using cone-beam measurements [Tuy 83], and second, the applied theory is a rather straightforward extension of the 2-D reconstruction theory to the 3-D geometry [Turb 01]. This adaption is incorrect in a strictly mathematical sense, but it still provides acceptable image quality in many medical and industrial application areas.

Recently, theoretically exact and stable<sup>1</sup> reconstruction algorithms have been developed providing excellent image quality without any cone artifacts and at the same time allowing an implementation in the computationally efficient FBP framework. Nevertheless, these algorithms have an increased computational complexity as they require additional computations for the filtering of the projection images, e.g. derivative computation and filtering along oblique lines in the projection. Thus, especially the filtering of projections incurs much more computations to be performed by the image reconstruction hardware. In order to apply these methods to cone-beam CT the data completeness condition must be ensured (see [Scho 01] for an overview of complete source trajectories). For example, appropriate trajectories are provided by a helical acquisition [Kats 03] or by extending the circular acquisition with an additional line [Kats 04] or arc segment [Kats 05].

The reconstruction task can also be solved in an entirely different way using iterative reconstruction methods. These methods start from an initial volume to be reconstructed. Then, a sequence of alternating forward-projections of the current reconstructed object and a corrective back-projection is performed until the reconstruction has converged to a solution that fits a certain convergence criterion. While iterative approaches are conceptually simpler than analytical approaches, they are computationally much more demanding, which has prohibited their use in most practical CT reconstruction systems up to now. However, in certain situations improved image quality can be achieved by using iterative approaches [Muel 98]. This is especially the case when a sufficiently large number of projections is not feasible or simply not desired to measure. Iterative approaches further achieve better image quality when the projections are not uniformly distributed over the scan trajectory. Statistical iterative reconstruction approaches have been used in molecular imaging scanners for a few years. In this domain it is possible to significantly improve the image quality for noisy data by incorporating physical effects of the acquisition process into the reconstruction algorithm.

<sup>&</sup>lt;sup>1</sup> A reconstruction algorithm is theoretically exact and stable when the reconstruction is consistent, i.e., identical to the ground truth when the algorithm is applied to noise-free data with infinite spatial and temporal resolution, and when the reconstruction is stable, i.e., robust for finite resolution effects and data noise [Noo 09].

## 1.2 Hardware Variants

The typical clinical workflow requires high-speed reconstructions in order to enable high patient throughput or to avoid an interruption of patient treatment during interventional procedures. From the physician's perspective, it is required that the computation of the reconstructed volume from a set of acquired two-dimensional X-ray projections terminates roughly with the end of the scanning period so that no additional time delay is experienced and the volume dataset can be analyzed immediately after the scan.

The computational complexity of the algorithms mentioned in the previous section depends linearly on both the number of projection images that are acquired during the scan period as well as the number of voxels of the volume dataset to be reconstructed. In order to fulfill the physician's challenging performance requirements, it is inevitable to employ fast compute hardware. There is in fact a variety of compute hardware that can be employed to design high-speed image reconstruction systems. We are going to evaluate following hardware variants in this thesis (see also Figure 1.2):

- 1. The amazing progress in VLSI design<sup>2</sup> has led to the development of microprocessors consisting of several independent compute cores that can execute multiple application tasks in parallel. The cores belonging to one central processing unit (CPU) often share certain levels of the on-chip memory hierarchy (e.g., on-chip Level 2 (L2) caches). These processors are commonly referred to as multi-core or even as many-core CPUs. Current CPU manufacturers such as Intel and AMD currently provide up to eight compute cores per CPU with forecasts predicting 32 and even more parallel cores per CPU chip.

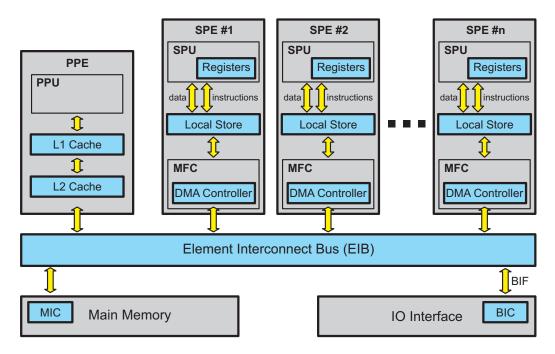

- 2. The Cell Broadband Engine Architecture (CBEA), which was developed by IBM, Sony, and Toshiba, represents a special member of the family of multi-core CPUs. The CBEA is characterized by an architecture that covers a control core as well as eight high-performance processing cores. While the CBEA primarily targets the gaming industry, it has been demonstrated that this architecture is suitable for various numerically intensive applications in industrial and medical environments as well.

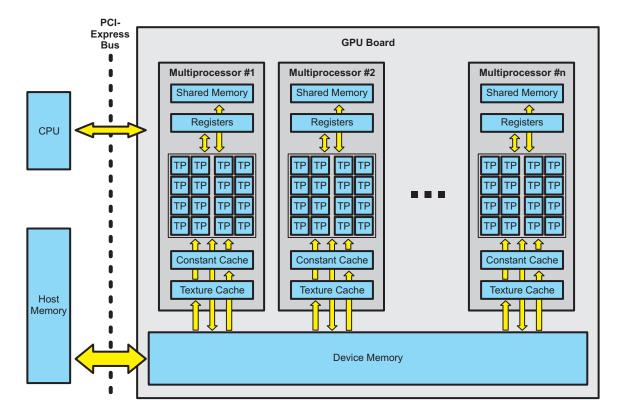

- 3. Standard graphics boards based on powerful graphics processing units (GPUs) can serve as another hardware alternative for high-performance computing applications. Current GPUs offer massively parallel processing capability that can particularly handle the computational complexity of three-dimensional conebeam reconstruction. Nvidia has recently developed the fundamentally new easy-to-use computing paradigm CUDA (Compute Unified Device Architecture) for solving complex computational problems on the GPU. CUDA offers a unified hardware and software solution for parallel computing on CUDA-capable Nvidia GPUs, supporting the standard C programming language together with high-performance computing numerical libraries<sup>3</sup>. This enables programmers

<sup>&</sup>lt;sup>2</sup> Very-large-scale integration (VLSI) is the process of creating integrated circuits by combining thousands of transistor-based circuits into a single chip.

<sup>&</sup>lt;sup>3</sup>http://developer.nvidia.com/object/cuda.html

Figure 1.2: Considered hardware variants. Image (a) is taken from http://www.intel.com/pressroom/kits/quadcore/index.htm, Image (b) is taken from http://en.wikipedia.org/wiki/File:Cell-Processor.jpg, and Image (d) is by courtesy of Siemens AG.

that are not specialists in computer graphics to benefit from the processing power of graphics cards. The implementation of the reconstruction task can now be accomplished without knowing how to (ab)use the existing application programming interfaces for general-purpose computing; e.g., OpenGL, DirectX, or the Brook language.

4. Reconfigurable microchips represent another architecture alternative for accelerating numerically intensive algorithms. FPGAs (field-programmable gate arrays) and CPLDs (complex programmable logic devices) are the most prominent representatives of reconfigurable circuits [Meye 08]. In general, FPGAs are characterized by a larger number of arithmetic units than CPLDs. Several independent vendors offer FPGA-based accelerator cards for use in general-purpose computer environments, along with appropriate development kits for software and firmware. Today, many CT devices employ FPGA hardware for

image reconstruction that has been developed by the manufacturer of the CT system itself in order to precisely meet the manufacturer's requirements.

## 1.3 Related Work

Published results using PC-based implementations still need more than several minutes for the reconstruction at high spatial resolution such as volumes of 512<sup>3</sup> voxels or even more [Wies 00, Yu 01, Kach 06]. Therefore, many specialized hardware platforms have been designed in the past to reconstruct volumes from cone-beam projections, ranging from dedicated hardware solutions like FPGAs [Trep 02, Godd 02, Heig 07] and "digital signal processors" (DSPs) [Neri 07, Lian 10] to clusters of workstations [Reim 96, Laur 98].

Recently, a flat-panel cone-beam back-projection was published using one of the two Cell processors of a dual Cell Blade [Kach 07]. The results are comparable to the performance of our Cell-based back-projection module in this thesis. The same implementation approach was used in [Yan 08, Xu 07] demonstrating a graphics-based implementation using OpenGL.

The most time-consuming operation in the inner loop of reconstruction is the ratio computation due to the non-linear perspective projection model. Our approach avoids image rectification as suggested by [Ridd 06] and used by [Kach 07, Yan 08, Xu 07] that leads to the elimination of the homogeneous division, but introduces an additional low-pass filtering operation on the projection.

In order to implement the back-projection on GPUs, OpenGL and shading languages are still used in many publications [Muel 07, Chur 07]. In comparison to the traditional graphics-based implementation methods, our CUDA-based implementation of cone-beam reconstruction has even a slightly improved reconstruction speed.

In [Hill 09] an interesting GPU-based reconstruction approach is demonstrated which does a high-speed reconstruction of an arbitrary volume slice on-demand when it is requested by the visualization software.

Only few publications, however, address all time-consuming reconstruction tasks, filtering and back-projection, in a single publication. Moreover, a direct comparison of these results is not always possible in an objective manner since different algorithms, datasets and acquisition geometries were used.

## 1.4 Scope and Main Contribution of this Thesis

This thesis presents a detailed overview of the aforementioned hardware platforms and their application to the three-dimensional image reconstruction task in CT.

In the first part of this thesis, we develop and evaluate an implementation approach for the most commonly used reconstruction algorithm in practical cone-beam CT scanners; the FDK method. We outline the challenges to implement this algorithm for real CT systems that usually deviate slightly from the ideal Feldkamp geometry. In this regard the main contribution of this thesis, however, can be classified as a thorough optimization and evaluation of computational performance using different hardware platforms. Several parallel implementations are developed – each of them is

specially suited for one of the mentioned acceleration devices. Our optimized implementation of the FDK method has been presented at the SPIE Medical Imaging Conference 2007 [Sche 07c] for the CBEA and for graphics accelerators at the IEEE Nuclear Science Symposium and Medical Imaging Conference 2007 [Sche 07b]. These implementations enable a novel reconstruction mode where an FDK reconstruction is computed on-the-fly at the same time the data is acquired by the C-arm device. The reconstructed volume can thus be shown to the physician in real time immediately after the last projection image has been acquired.

During our evaluations we use the same two medical datasets, which were acquired using a standard C-arm device, on each of the considered hardware platforms. Therefore, we are able to present a fair comparison of the currently most promising hardware variants in the context of cone-beam reconstruction. This is a novel practice since we use the same implementation approach of the FDK method – suitable for practical cone-beam CT scanners – and the same datasets for the evaluation of several state-of-the-art hardware architectures. This comparative study has been submitted to the Journal of Medical Physics.

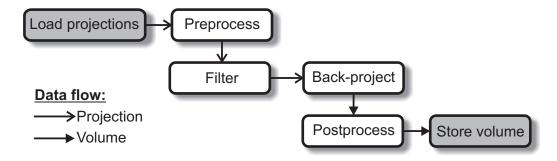

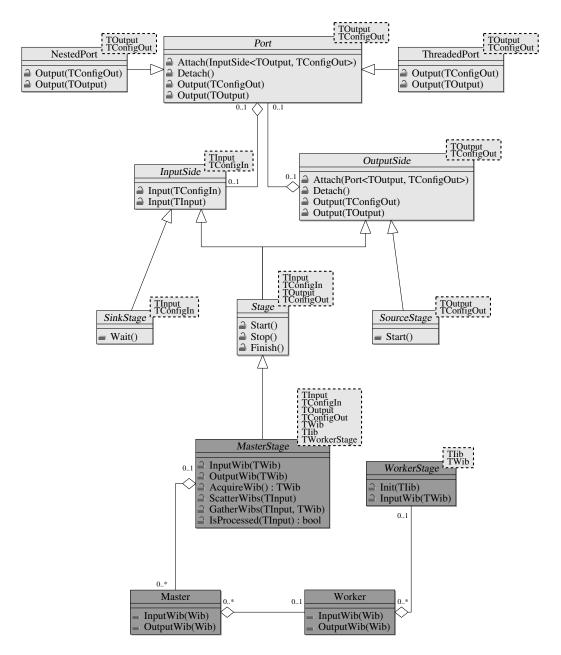

We further present both the design and the implementation of a software architecture that is used by all of our optimized implementations. Software engineering techniques play an important role in the overall design and can improve the efficiency, flexibility, and portability of the whole reconstruction system. We show how this design can act as a hardware abstraction layer on top of different acceleration architectures. The design and implementation of our software architecture has been presented at the International Conference on Software Engineering 2008 [Sche 08].

Since the FDK method is of an approximative nature, its reconstruction results suffer from severe artifacts in certain situations. In the second part of this thesis we select two alternative approaches to cone-beam reconstruction, which are able to deliver significantly improved image quality when compared to the results of the FDK method.

We show for the first time a highly optimized implementation of a theoretically exact and stable FBP algorithm. We select the M-line method, which is well suited for the non-ideal acquisitions in practical cone-beam CT scanners, and at the same time totally resolves the problem of cone artifacts in FDK reconstructions. We further demonstrate on-the-fly reconstruction on a dual Cell Blade using our optimized CBEA-based implementation. The performance-optimized version of the M-line method has been presented at the International Meeting on Fully Three-Dimensional Image Reconstruction in Radiology and Nuclear Medicine 2007 [Sche 07a].

Additionally, we present an iterative reconstruction approach with a strong focus on the CUDA-based optimization of its most time-consuming processing steps; the forward-projection and the back-projection. Iterative approaches can be used when analytic algorithms such as the FDK method and the M-line method do not achieve good image quality. For example this is the case when a sufficiently large number of projections is not feasible or simply not desired to measure. Iterative approaches have also the opportunity to achieve better image quality when the projections are not uniformly distributed over the scan trajectory. Our optimized CUDA-based implementation of the forward- and back-projection module has been presented at the International Workshop on New Frontiers in High-performance and Hardware-aware

Computing 2008 [Wein 08] and at the IEEE Nuclear Science Symposium and Medical Imaging Conference 2009 [Keck 09a]. Furthermore, our optimized implementations of both the forward- and the back-projection are used in an ongoing research project at the University of Erlangen-Nuremberg, Chair of Computer Science 5 (Pattern Recognition) [Keck 09b].

## 1.5 Outline

The structure of this thesis is as follows. Chapter 2 describes several reconstruction methods for computing a volumetric representation of a scanned object from a set of two-dimensional X-ray projection images. In particular we present the approximate FDK method (Section 2.2), the theoretically exact and stable M-line method applied to a short-scan circle-plus-arc acquisition (Section 2.3.1) and the simultaneous algebraic reconstruction technique as a representative of the iterative approaches (Section 2.3.2).

Chapter 3 contains an overview of the underlying software layer that we have developed in order to facilitate the integration of hardware accelerators into our image reconstruction software infrastructure.

The architectures of the considered hardware variants and efficient implementations of the FDK reconstruction method on these hardware platforms are presented in Chapters 5 to 7. Each Chapter addresses a single hardware architecture.

In Chapter 4, we discuss our CBEA-based implementation and present corresponding performance results. Chapter 5 then focuses on multi-core CPUs and again summarizes our results. In Chapter 6, we outline CUDA-based implementations on Nvidia graphics cards. Chapter 7 contains a description of a highly efficient implementation using the FPGA-based hardware accelerator platform ImageProX, which was developed by Siemens Healthcare.

In the following chapter (Chapter 8) we focus on two alternative reconstruction algorithms. In particular we present a highly optimized CBEA-based implementation of the M-line method (Section 8.1) and a CUDA-accelerated version of the most computationally demanding processing steps of an iterative method (Section 8.2).

Finally, in Chapter 9, we compare our results, draw our final conclusions, and discuss possible future directions of research in the field of hardware-accelerated conebeam CT reconstruction.

# Chapter 2

# Algorithms for Cone-Beam Image Reconstruction

There exist several reconstruction methods for computing a volumetric representation of a scanned object from a set of two-dimensional X-ray projection images. However, the most commonly applied method in practical cone-beam CT systems is the approximate FDK method. After we give some prerequisites that are necessary to understand the following descriptions, we present in Section 2.2 the FDK method, discuss possible implementation strategies (Section 2.2.2) that can be applied to practical cone-beam systems and analyze the time complexity of the involved algorithmic steps (Section 2.2.3).

Although many CT systems use the FDK method to solve the 3-D image reconstruction task, it is not without its short-comings. Therefore, we describe in Section 2.3 two alternative approaches: the theoretically exact and stable M-line method applied to a short-scan circle-plus-arc acquisition (Section 2.3.1) and the simultaneous algebraic reconstruction technique as a representative of the iterative approaches (Section 2.3.2). The M-line method totally resolves the problem of cone artifacts, which result from the approximative nature of the FDK method. Iterative approaches can be used when analytic algorithms such as the FDK method and the M-line method do not achieve good image quality. For example this is the case when a sufficiently large number of projections is not feasible or simply not desired to measure. Iterative approaches also have the opportunity to achieve better image quality when the projections are not uniformly distributed over the scan trajectory.

## 2.1 Prerequisites

The task in 3-D image reconstruction is to recover the function of X-ray attenuation coefficients f(x) of an object under examination, provided a set of line integrals

$$g(\lambda, \underline{\theta}) = \int_0^\infty f(\underline{a}(\lambda) + t\underline{\theta})dt.$$

(2.1)

Here, the 3-D curve  $\underline{a}(\lambda)$  describes the corresponding position of the X-ray source with  $\lambda$  varying over a finite interval of  $\mathbb{R}$ , and the unit vector  $\underline{\theta}$  represents the direction of the respective ray.

If we assume a flat-panel detector located at a distance D from the current source position, each detector value at coordinates  $(u,v)^T$  refers to an integral along a straight line with direction

$$\underline{\theta}(u,v) = \left(u\underline{e}_u + v\underline{e}_v - D\underline{e}_w\right) / \sqrt{u^2 + v^2 + D^2}. \tag{2.2}$$

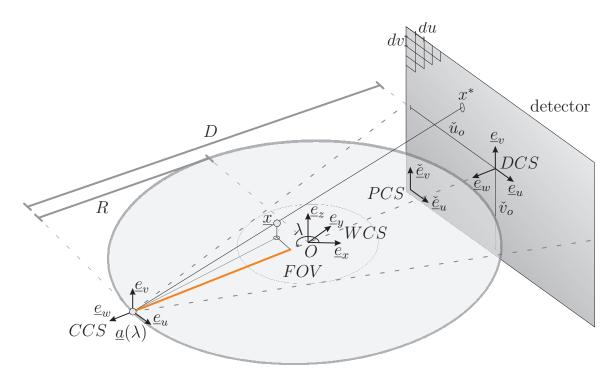

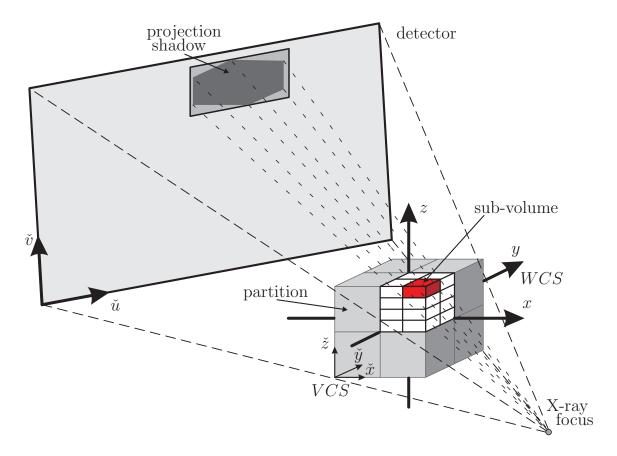

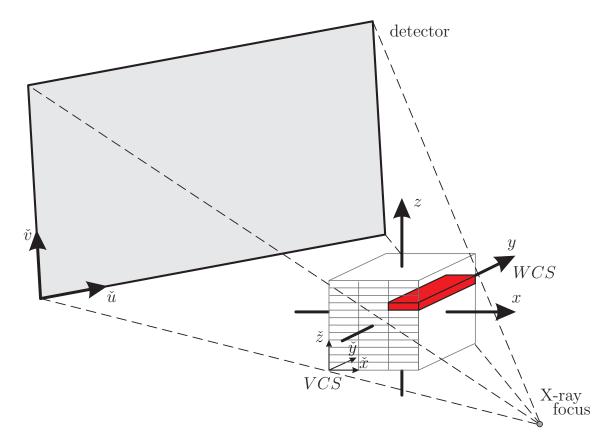

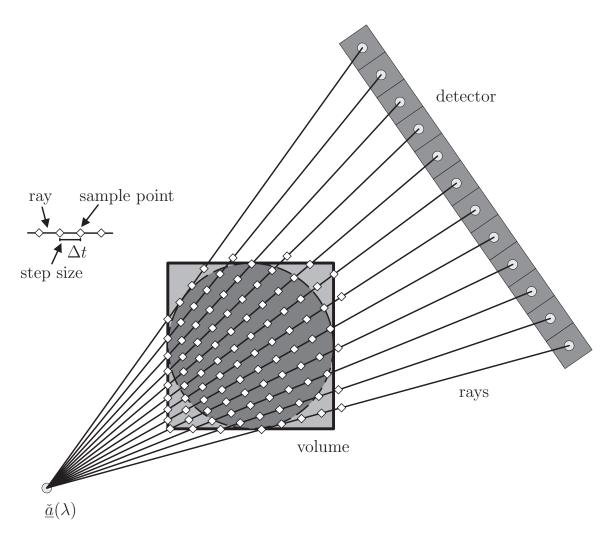

Here, the detector coordinates are identified by two orthogonal unit vectors  $\underline{e}_u$  and  $\underline{e}_v$ , and the origin  $(0,0)^T$  of the detector coordinate system (DCS) is the orthogonal projection of  $\underline{a}(\lambda)$  onto the detector. The unit vector  $\underline{e}_w = \underline{e}_u \times \underline{e}_v$  points from the origin of the DCS towards the source position. The ray that hits the detector at the origin of the detector coordinate system is commonly referred to as principal ray, while the respective intersection point is usually referred to as principal point. The set of rays corresponding to a certain source position  $a(\lambda)$  and a certain flat-panel detector position thus geometrically forms a cone-beam. Throughout this thesis we refer to the resulting 2-D X-ray images as cone-beam projections. This scan geometry is illustrated in Figure 2.1.

#### The Feldkamp Algorithm 2.2

In 1984, Feldkamp, Davis, and Kress published an algorithm for circular cone-beam tomography, which is still widely used in state-of-the-art cone-beam scanning devices; e.g., C-arm CT. This algorithm is usually referred to as Feldkamp method or as FDK method [Feld 84]. It represents an analytical 3-D reconstruction method resulting in a filtered back-projection scheme. It can be understood as an extension of exact 2-D reconstruction algorithms for fan-beam projections [Kak 01] to the 3-D case by properly adapting the weighting factors.

The Feldkamp algorithm is based upon a circular trajectory, as is shown in Figure 2.1. The X-ray source rotates along an ideal circle of radius R with center point O in the midplane about the axis of rotation that is defined by the point O and the direction  $\underline{e}_z$ . Each point  $\underline{a}(\lambda)$  on the source trajectory with  $\lambda$  representing the rotation angle of the source-detector assembly expressed in radians is thus given by the vector

$$\underline{a}(\lambda) = (R\cos\lambda, R\sin\lambda, 0)^T \text{ for } \lambda \in [0, 2\pi[,$$

(2.3)

where the coordinates on the right-hand side refer to the fixed right-handed world coordinate system defined by its origin O and the unit vectors  $\underline{e}_x$ ,  $\underline{e}_y$ , and  $\underline{e}_z$ . Then, the aforementioned unit vectors  $\underline{e}_{u}$ ,  $\underline{e}_{v}$  and  $\underline{e}_{w}$  are given as the rotated coordinate axes

$$\underline{e}_u(\lambda) = (-\sin \lambda, \cos \lambda, 0)^T,$$

(2.4)

$$\underline{e}_v = (0,0,1)^T, \qquad (2.5)$$

$$\underline{e}_{u}(\lambda) = (-\sin \lambda, \cos \lambda, 0)^{T}, \qquad (2.4)$$

$$\underline{e}_{v} = (0, 0, 1)^{T}, \qquad (2.5)$$

$$\underline{e}_{w}(\lambda) = (\cos \lambda, \sin \lambda, 0)^{T} = \underline{e}_{u}(\lambda) \times \underline{e}_{v}, \qquad (2.6)$$

where the coordinates on the right-hand sides again refer to the fixed world coordinate system. As is illustrated in Figure 2.1, these axes are obtained from the x-, y- and

Figure 2.1: Ideal Feldkamp geometry. The X-ray source rotates along an ideal circle of radius R with center point O in the midplane about the axis of rotation that is defined by the point O and the direction  $\underline{e}_z$ . The rotation direction is given by the angle  $\lambda$  in counterclockwise direction. D is the orthogonal distance between  $\underline{a}(\lambda)$  and the corresponding detector plane. Four different coordinate systems are shown: the world coordinate system (WCS), the camera coordinate system (CCS), the detector coordinate system (DCS), and the pixel coordinate system (PCS). The voxel coordinate system (VCS) is not shown in this figure. The cylindrical field-of-view (FOV) is indicated by the inner circle. Only points inside the FOV can be reconstructed.

z-axes by a rotation of angle  $\pi/2 + \lambda$  about the z-axis in counter-clockwise direction and then flipping the direction of  $\underline{e}_w(\lambda)$ .

Throughout this thesis we use the notation ":" to denote quantities that refer to coordinates of the pixel coordinate system (PCS) or the voxel coordinate system (VCS).

## 2.2.1 Algorithmic Steps

In order to approximately reconstruct a value  $f(\underline{x})$  at any position  $\underline{x} = (x, y, z)$  within the support of the object density function f using the Feldkamp algorithm, the following algorithmic steps must be applied successively<sup>1</sup>.

<sup>&</sup>lt;sup>1</sup> Note that the Feldkamp algorithm is only an approximate method for 3-D reconstruction. This results from the fact that a circular scan trajectory necessarily leads to an incomplete sampling of the Radon space, see [Feld 84].

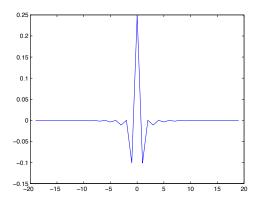

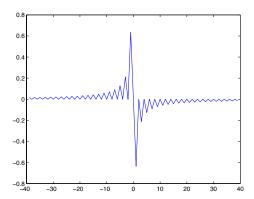

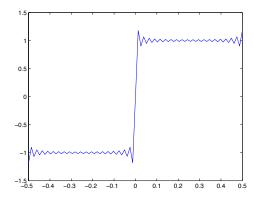

Figure 2.2: Illustration of the ramp filter  $h_{ramp}$ . On the left side the impulse response of the ramp filter is shown. On the right side the ideal filter response is shown in the frequency domain. It has been band-limited to 1/(2 du). Here, du denotes the width of a pixel in direction  $\underline{e}_u$ .

Step 1 – Filtering. Each projection  $g(\lambda, \underline{\theta}(u, v))$  is transformed into a filtered projection  $g^F(\lambda, u, v)$  according to the following steps F1 and F2:

F1 – Cosine Weighting. Weight the data according to

$$g_1(\lambda, u, v) = \frac{D}{\sqrt{u^2 + v^2 + D^2}} g(\lambda, \underline{\theta}(u, v)), \qquad (2.7)$$

where the factor  $D/\sqrt{u^2+v^2+D^2}$  represents the cosine of the angle between the principle ray of the cone-beam hitting the detector at the origin of the DCS and the ray hitting the detector at position  $(u, v)^T$ , see again Figure 2.1.

$\mathbf{F2} - \mathbf{Ramp}$  Filtering. Ramp-filter the projection images row-wise (i.e., with respect to u) by computing

$$g^{F}(\lambda, u, v) = g_1(\lambda, u, v) * h_{ramp}(u), \qquad (2.8)$$

where  $h_{ramp}$  denotes the ideal ramp filter (see Figure 2.2) and "\*" denotes the convolution operator. This step corresponds to a 1-D convolution along lines on the detector that are parallel to  $\underline{e}_u(\lambda)$ .

Step 2 – Back-Projection. Back-project the filtered projection  $g^F(\lambda, u, v)$  into the image space to obtain an approximation  $\hat{f}$  of f at each point x according to

$$\hat{f}(\underline{x}) = \frac{1}{2} \int_0^{2\pi} \mu(\lambda, \underline{x}) g^F(\lambda, u(\lambda, \underline{x}), v(\lambda, \underline{x})) d\lambda, \qquad (2.9)$$

where u and v are the respective detector coordinates given by

$$u(\lambda, \underline{x}) = -D \frac{\langle (\underline{x} - \underline{a}(\lambda)), \underline{e}_u \rangle}{\langle (\underline{x} - \underline{a}(\lambda)), \underline{e}_w \rangle}, \qquad (2.10)$$

$$v(\lambda, \underline{x}) = -D \frac{\langle (\underline{x} - \underline{a}(\lambda)), \underline{e}_v \rangle}{\langle (\underline{x} - \underline{a}(\lambda)), \underline{e}_w \rangle}, \qquad (2.11)$$

and  $\mu(\lambda, \underline{x})$  is a point-dependent distance weight according to

$$\mu(\lambda, \underline{x}) = \frac{R^2}{\langle (\underline{x} - \underline{a}(\lambda)), \underline{e}_w \rangle^2}.$$

(2.12)

Here,  $\langle .,. \rangle$  denotes the inner product. For a detailed derivation, we refer to [Kak 01]. For short-scan acquisitions the back-projection interval has to be restricted to the covered angular range of the scan, and before the computation of (F1) an additional data redundancy weighting step, which is commonly referred to as (generalized) Parker weighting [Silv 00, Park 82] has to be applied.

In order to assess the performance using the acceleration architectures under consideration, we restrict our evaluation to the most compute-intensive algorithmic tasks; the ramp filtering step (F2) as well as the back-projection step (Step 2).

## 2.2.2 Implementation Strategies

#### 2.2.2.1 Ramp Filtering

The FDK reconstruction approach requires to filter the rows of the projections using a high-pass filter in the direction of  $\underline{e}_u$ . An ideal acquisition would ensure that the vector  $\underline{e}_u$  and thus the detector rows be parallel to the plane of the source trajectory. In practical cone-beam CT systems such as C-arm scanners this assumption may be violated due to deviations caused by mechanical inaccuracies during the acquisition process. However, we perform the ramp filtering step in the direction of the detector rows, regardless of any reconstruction inaccuracies introduced by this assumption of an ideal scan geometry<sup>2</sup>.

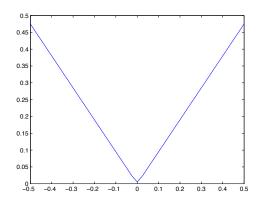

Various filter kernels are used in practice; e.g. combinations of ramp filters and smoothing filters. Due to the typical filter mask sizes of 60 non-zero elements and more, convolutions are practically computed in the Fourier domain due to the reduced computational complexity. For example, considering the number of required floating-point operations for convolving a single image row with 1024 pixels the break-even point is already reached when filter mask sizes are larger than 17 pixels (see Section 2.2.3 for further details).

As is explained in detail in [Kak 01], this convolution algorithm requires the computation of the discrete Fourier transform (DFT) of each input signal (projection row) as well as the DFT of the spatial filter kernel. The actual convolution of any two vectors in Fourier space is then performed by component-wise multiplication of their Fourier components. Then, the inverse DFT (IDFT) of this product is computed in order to transform the filtered projection rows back into the spatial domain. The input vectors and the filter kernels are zero-padded up to a suitable power of two in order to avoid aliasing effects that may severely spoil the results [Gonz 08]. Throughout this thesis we denote by convolution length the zero-padded size of the input vector or filter kernel.

$<sup>^2</sup>$  In a non-ideal scan geometry it is possible that the detector rows and thus the vector  $\underline{e}_u$  are slightly tilted with respect to an ideal Feldkamp-like acquisition. In such a situation the vector  $\underline{e}_u$  and the geometrical parameters of the X-ray camera and the detector can be extracted from the corresponding projection matrix (see Appendix A), which is usually determined by calibration. See e.g. [Wies 00] for more details.

On the considered hardware platforms, computationally efficient FFT cores are available for the calculation of complex fast Fourier transforms (FFT). Since it is possible to compute the Fourier-based convolution for two (real-valued) input vectors simultaneously using complex FFTs, we always convolve two adjacent image rows of a projection with the given filter kernel simultaneously. One image row defines the real input while the second one refers to the imaginary input. All of our optimized implementations compute the convolution by a complex 1-D FFT followed by the point-wise multiplication of the DFT of the filter kernel and the computation of the inverse FFT (IFFT) of the respective point-wise product.

#### 2.2.2.2 Back-Projection

Back-projection can either be implemented using a voxel- or a ray-driven volume update strategy.

In the ray-driven approach it is required to follow the rays defined by the pixels in the projection image to the source position through the volume. Each affected volume voxel gets an appropriate weighted increment depending on how much the current ray affects the respective voxel. This approach, however, is hard to parallelize for the considered hardware platforms. Each time a voxel is hit by a ray and thus gets updated, it must be ensured that no other ray does an update of that voxel at the same time. Otherwise wrong voxel accumulation may occur due to race conditions during voxel read/write accesses. Moreover, ray-based back-projection approaches tend to introduce high-frequency artifacts that manifest as Moire patterns in the final reconstruction result [De M 02, De M 04].

For these reasons, we decided to implement the voxel-driven back-projection scheme on the considered acceleration hardware. Each voxel can be updated independently by calculating the detector position where the ray emanating from the source and passing the considered voxel center hits the projection image. This results in an embarrassingly parallel problem, because projection values are accessed read-only, and all voxel accesses for the same projection are independent of each other.

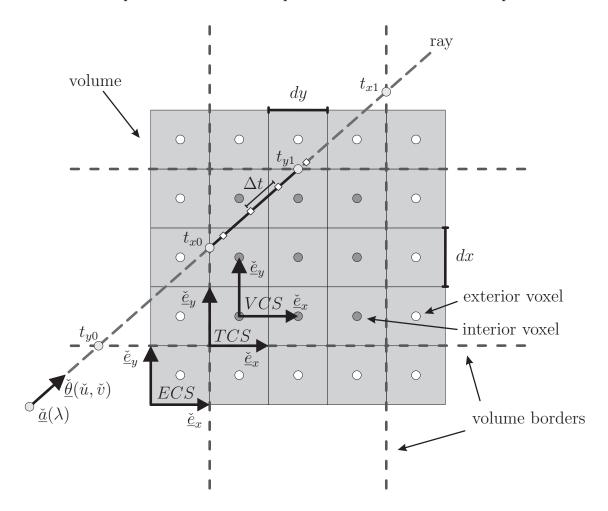

Because of deviations due to mechanical inaccuracies of real cone-beam CT systems such as mobile and stationary mounted C-arm scanners, the back-projection is commonly not computed using Equations (2.9), (2.10), and (2.11) directly. Instead, the mapping between voxels of the volume and projection image positions can be described by introducing homogeneous coordinates and a corresponding  $3 \times 4$  projection matrix  $\mathbf{P}(\lambda)$  for each X-ray source position  $\underline{a}(\lambda)$  at rotation angle  $\lambda$  along the trajectory [Hart 03]. The projection matrices are commonly estimated during a calibration step that must be accomplished only when the cone-beam CT scanner is installed or maintained. See for example Wiesent et al. [Wies 00] for more details about the calibration of cone-beam CT systems.

In an ideal geometry as described in Section 2.2, the projection matrices operating on points given in world coordinates can be calculated analytically from Equations (2.10) and (2.11):

$$\tilde{\mathbf{P}}(\lambda) = \begin{bmatrix} -D\sin\lambda & D\cos\lambda & 0 & 0\\ 0 & 0 & D & 0\\ -\cos\lambda & -\sin\lambda & 0 & R \end{bmatrix}.$$

(2.13)

In order to express the resulting detector coordinates with respect to the PCS, the necessary transformations can be applied by multiplying a  $3 \times 3$  matrix  $\tilde{\mathbf{K}}(\lambda)$  to the projection matrix of Equation (2.13) from the left<sup>3</sup>:

$$\mathbf{P}(\lambda) = \tilde{\mathbf{K}}(\lambda)\tilde{\mathbf{P}}(\lambda) = \begin{bmatrix} \frac{1}{du} & 0 & \check{u}_o \\ 0 & \frac{1}{dv} & \check{v}_o \\ 0 & 0 & 1 \end{bmatrix} \tilde{\mathbf{P}}(\lambda).$$

(2.14)

Here, du and dv denote the pixel width in u-direction and v-direction of the detector, respectively. See Figure 2.1 for a clarification of the symbols used in Equations (2.13) and (2.14). This step transforms world coordinates into pixel coordinates and translates any possible offset of the principal point. See Appendix A for further details.

Likewise the projection matrix can be modified by multiplying a  $4 \times 4$ -matrix from the right in order to include the necessary transformations from voxel coordinates to world coordinates. This transform comprises the necessary scaling and translation of the voxel coordinates to a representation in the world coordinate system:

$$\mathbf{T}(\lambda) = \begin{bmatrix} dx & 0 & 0 & t_x \\ 0 & dy & 0 & t_y \\ 0 & 0 & dz & t_z \\ 0 & 0 & 0 & 1 \end{bmatrix}. \tag{2.15}$$

Here, dx, dy, and dz denote the voxel widths in x-, y-, and z-direction of the world coordinate system, respectively, while  $t_x$ ,  $t_y$ , and  $t_z$  represent the translation of the voxel coordinate system relative to the world coordinate system in units of world coordinates.

The final projection matrix operating on points given in voxel coordinates in an ideal Feldkamp-like acquisition is then given as

$$\check{\mathbf{P}}(\lambda) = \mathbf{P}(\lambda)\mathbf{T}(\lambda). \tag{2.16}$$

Back-projection may now be computed by calculating a matrix-vector product for each voxel and each projection in order to determine the corresponding homogeneous representation of the projection value, followed by the homogeneous division to reveal the actual detector position (see Algorithm 1)<sup>4</sup>. The intermediate results  $\check{u}$  and  $\check{v}$  represent detector positions given as column index and row index, respectively, as non-integer numbers. The computation of the actual voxel increment is hidden behind the function "fetch" that may be based on nearest neighbor or bilinear interpolation of the filtered projection values, for example.

<sup>&</sup>lt;sup>3</sup>Note that in an ideal setting  $\tilde{\mathbf{K}}(\lambda)$  covers a scaling operation and a translation operation only. <sup>4</sup>Any matrix entry is referenced by its row index and its column index.  $\mathbf{P}[i, j]$  thus refers to the

<sup>\*</sup>Any matrix entry is referenced by its row index and its column index. P[i, j] thus refers to the entry in the *i*th row and the *j*th column. Throughout this thesis, arrays are assumed to be 0-based. Consequently, P[0, 0] refers to the upper left entry of matrix P.

#### **Algorithm 1:** Voxel-driven back-projection.

```

Input: N_p filtered projection images I_i, 0 \le i < N_p

Input: N_p projection matrices \dot{\mathbf{P}}_i, 0 \le i < N_p

Data: volume V consisting of N_x \times N_y \times N_z voxels

1 for (i = 0; i < N_p; i = i + 1) do

for (\check{z} = 0; \check{z} < N_z; \check{z} = \check{z} + 1) do

2

for (\check{y} = 0; \check{y} < N_u; \check{y} = \check{y} + 1) do

3

for (\check{x} = 0; \check{x} < N_x; \check{x} = \check{x} + 1) do

4

// Compute homogeneous image coordinates

r = \check{\mathbf{P}}_{i}[0,0] \cdot \check{x} + \check{\mathbf{P}}_{i}[0,1] \cdot \check{y} + \check{\mathbf{P}}_{i}[0,2] \cdot \check{z} + \check{\mathbf{P}}_{i}[0,3];

5

s = \check{\mathbf{P}}_{i}[1,0] \cdot \check{x} + \check{\mathbf{P}}_{i}[1,1] \cdot \check{y} + \check{\mathbf{P}}_{i}[1,2] \cdot \check{z} + \check{\mathbf{P}}_{i}[1,3];

6

t = \check{\mathbf{P}}_{i}[2,0] \cdot \check{x} + \check{\mathbf{P}}_{i}[2,1] \cdot \check{y} + \check{\mathbf{P}}_{i}[2,2] \cdot \check{z} + \check{\mathbf{P}}_{i}[2,3];

7

\begin{split} t_{inv} &= 1/t;\\ \check{u} &= r \cdot t_{inv};\\ \check{v} &= s \cdot t_{inv};\\ \mu &= t_{inv} \cdot t_{inv}; \end{split}

8

// Dehomogenize

9

// Dehomogenize

10

// Distance weight

11

\mathbf{V}[\check{x},\check{y},\check{z}] = \mathbf{V}[\check{x},\check{y},\check{z}] + \mu \cdot \text{fetch}(I_i,\check{u},\check{v});

// Accumulate

12

end

13

end

14

end

15

16 end

```

For neighboring voxels, it is sufficient to increment the homogeneous detector coordinates by the appropriate column of  $\check{\mathbf{P}}(\lambda)$  [Wies 00]. Algorithm 2 shows the pseudo-code for the computationally optimized version (incremental version) of the back-projection step. First, we calculate in each loop the base increment for the homogeneous detector coordinates. Then, in each loop we multiply the actual voxel index with the respective voxel increments before adding them to the base increments of the current loop. This approach requires an additional floating-point multiplication for each voxel to compute the homogeneous detector coordinates. We avoid to simply increment the actual computed homogeneous detector coordinates, which would save the additional floating-point operation but introduces numerical problems. The hardware variants, which we consider throughout this thesis, provide a special multiply-add floating-point operation such that both approaches require only a single instruction.

The homogeneous divide operation in Algorithm 2 cannot be avoided for voxel position increments parallel to the z-axis of the VCS because, in practical cone-beam CT systems, the projection planes are slightly tilted with respect to the z-axis due mechanical inaccuracies. We intentionally avoided the use of a detector rebinning technique that virtually aligns the detector to one of the volume axis because it impairs the resulting image quality and requires additional computations for the initial rebinning step [Ridd 06].

Note that, in Algorithm 1 and Algorithm 2, the voxel-specific distance weight  $\mu = \mu(\lambda, \underline{x})$  is determined by exploiting a computational trick. Since each projection

matrix  $\mathbf{P}(\lambda)$  is only defined up to a scale factor, we normalize  $\mathbf{P}(\lambda)$  such that  $\mathbf{P}(\lambda)[2,3] = 1$ . In this case, it follows from Equations (2.12) and (2.14) that

$$\mu(\lambda, \underline{x}) = \frac{R^2}{\langle (\underline{x} - \underline{a}(\lambda)), \underline{e}_w \rangle^2} = \frac{1}{t^2}.$$

(2.17)

Consequently, only one additional multiply operation is necessary to compute the distance weight itself (i.e.,  $t^{-1} \cdot t^{-1}$ ) and another one to compute the weighted voxel increment  $\mu \cdot \text{fetch}(I_i, \check{u}, \check{v})$  afterwards.

### 2.2.3 Complexity Analysis

In the last section we presented implementation approaches for the two most timeconsuming processing steps of filtered back-projection algorithms; the filtering step as well as the subsequent back-projection step. In this section we will analyze their time complexity.

#### 2.2.3.1 Filtering

As mentioned in Section 2.2.2.1 the filtering step can be implemented in the spatial or in the frequency domain. In the following we estimate the number of required floating-point operations required to implement each variant.

In the spatial domain the 1-D discrete convolution of the image rows of g with a filter kernel given as a 1-D mask h and consisting of  $N_M = 2m + 1$  elements (cf. Equation 2.8) can be computed by

$$g(\check{u}, \check{v}) = \sum_{k=-m}^{m} h(k)g(\check{u} - k, \check{v}).$$

(2.18)

The convolution for an image pixel requires one multiplication and one addition for each mask element, which results in

$$N_{spatial} = 2N_M N_u N_v N_p \tag{2.19}$$

floating-point operations for  $N_p$  projection images consisting of  $N_v$  rows and  $N_u$  columns. With  $N = N_u = N_v = N_p$  the discrete 1-D convolution of the projection image rows in the spatial domain has a time complexity of  $\mathcal{O}(N^3)$  for filter kernels with fixed impulse.

In the following we analyze the number of required floating-point operations when computing the 1-D convolution in the frequency domain. In order to transform an image row into the frequency domain and back to the spatial domain two FFTs have to be computed. The classic "radix-2" algorithm presented by Cooley and Tukey [Cool 65] requires a number of floating-point operations for the computation of a 1-D complex FFT that is proportional to  $5N\log_2 N$ . A more optimized variant has been published by [John 07]. Here, the number of required floating-point operations is only

$$N_{FFT} = \frac{34}{9} N \log_2 N - \frac{124}{27} N - 2 \log_2 N - \frac{2}{9} (-1)^{\log_2 N} \log_2 N + \frac{16}{27} (-1)^{\log_2 N} + 8 \quad (2.20)$$

Figure 2.3: Comparison of computational efficiency for spatial- and frequency-based convolution filtering. The break-even point is given as the largest filter mask size where convolution filtering in the spatial domain is still superior than frequency-based convolution. When using larger filter mask sizes frequency-based convolution is more efficient. The break-even points are given for two well-known FFT implementations.

for a convolution length of  $N_{conv} = N$ . Due to zero-padding  $N_{conv}$  is usually chosen such that  $N_{conv} = 2N_u$ . The complex multiplication in the frequency domain requires only two additions and two multiplications for each computed complex frequency value since the used filter kernels have either only real values or imaginary values in the frequency domain. As already mentioned in Section 2.2.2.1 it is possible to compute the Fourier-based convolution for two (real-valued) input vectors simultaneously using complex FFTs. Therefore,

$$N_{frequency} = N_{FFT} + 4N_{conv} (2.21)$$

floating-point operations are required for a single input vector resulting in a time complexity of  $\mathcal{O}(N^3 \log_2 N)$  when  $N = N_{conv} = N_u = N_v = N_p$ .

Figure 2.3 shows the break-even points for various convolution length according to our analysis. Therefore, it is more efficient to implement a 1-D convolution in the frequency domain if filter mask sizes are larger than 19 pixels when  $N_{conv} = 2048$  or 21 pixels when  $N_{conv} = 4096$ .

#### 2.2.3.2 Back-Projection

The time complexity of back-projection is significantly higher. In our voxel-based approach it is necessary to compute the back-projection for each voxel of the volume  $(N_{voxels} = N_x N_y N_z)$  and each projection image  $N_p$ . The number of voxels in

each direction usually equals the number of projection images  $(N_x = N_y = N_z = N_p)$ . Therefore, the time complexity of back-projection is  $\mathcal{O}(N^4)$ .

The voxel-based back-projection according to Algorithm 1 requires for each voxel nine multiplications and nine additions to compute the matrix vector product, two multiplications and two divisions for the computation of the pixel coordinates (dehomogenize), two multiplications to apply the voxel-dependent distance weight, and one addition to add the computed voxel increment to the previous voxel value. Therefore, the back-projection of a single projection image requires

$$N_{Bp} = (24 + N_i)N_{voxels} (2.22)$$

floating-point operations. Here,  $N_i$  is the number of floating-point operations that are required for the interpolation when accessing the projection image (function fetch in Algorithm 1).

Nearest neighbor interpolation can be implemented by incrementing the computed coordinates  $\check{u}$  and  $\check{v}$  by 0.5 before they are truncated to integer numbers. This increment can be integrated into the projection matrix as a translation of the PCS, and thus  $N_i=0$  for nearest neighbor interpolation. However, for bilinear interpolation  $N_i=10$  (six additions and four multiplications). Note that some hardware architectures, e.g. graphics accelerators, implement this operation in hardware resulting in  $N_i=1$  or even  $N_i=0$ .

The number of required floating-point operations can be significantly reduced when using the incremental version of Algorithm 2. By the incremental computation of the matrix vector product six multiplications and six additions are moved out of the innermost loop. Therefore, the back-projection of a single projection image now requires only

$$N_{BpIncr} = (12 + N_i)N_{voxels} + 6N_yN_z + 6N_z$$

(2.23)

floating-point operations. Compared to Algorithm 1 this reduces the number of required floating-point operations by over 35% when  $N_i = 10$  or by nearly 50% when  $N_i = 0$ .

#### 2.2.3.3 Comparison of Computation Times

Heigl and Kowarschik presented a performance analysis considering all processing steps in a practical C-arm CT system [Heig 07]. They measured relative timings of each processing task on a single-core CPU for 543 projection images with  $1240 \times 960$  pixels each and a volume consisting of  $512 \times 512 \times 440$  voxels.

Table 2.1 shows the time fractions of the particular algorithmic steps. The preprocessing tasks include intensity and beam hardening correction, scatter estimation and correction, and truncation correction, while post-processing includes the suppression of ring artifacts, which are caused by detector gain inhomogeneities. The pre-processing and post-processing steps, which are not considered in this thesis, take only 10% of the overall processing time. Therefore, our evaluation of filtering and back-projection on different hardware acceleration platforms addresses over 90% of the computational burden in a typical cone-beam CT system.

## 2.3 Selected Alternatives to the Feldkamp Algorithm

#### 2.3.1 The M-Line Method

In medical imaging a high image quality is required. In the state-of-the-art FDK method [Feld 84], however, the occurring cone artifacts may cover small object details complicating their distinction.

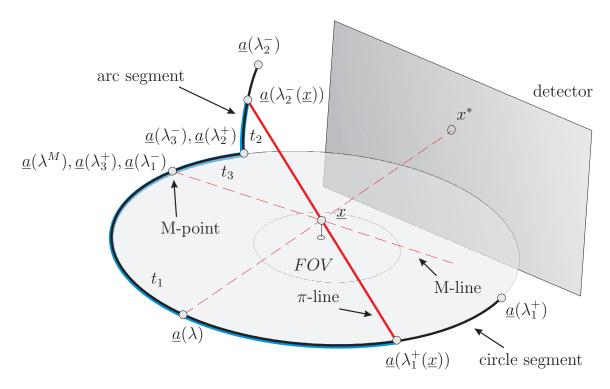

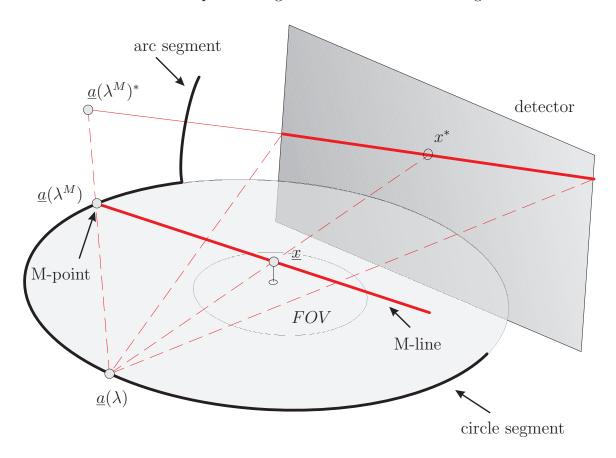

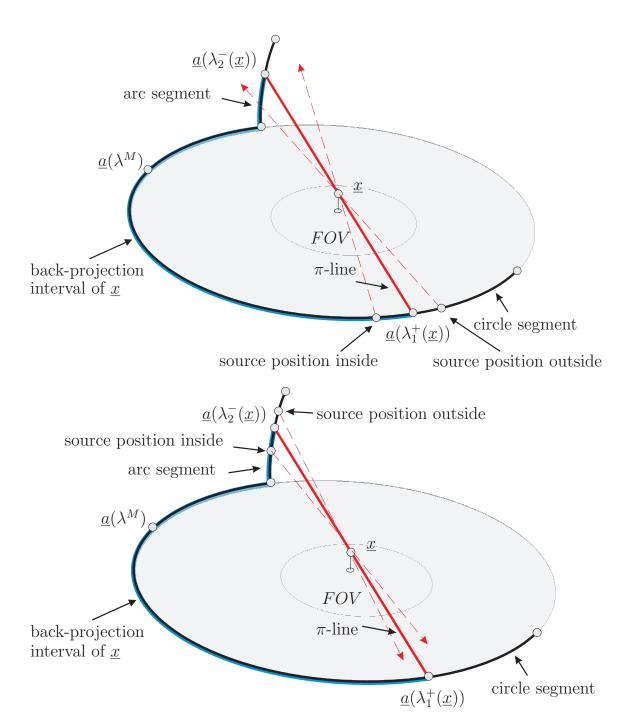

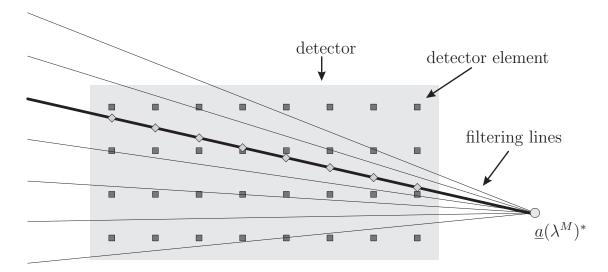

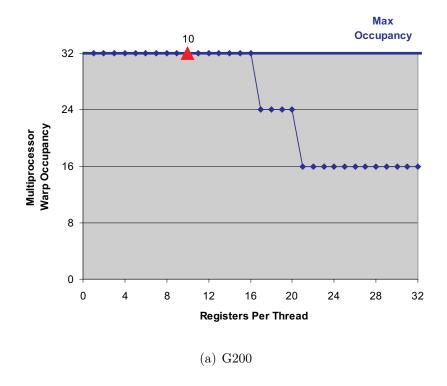

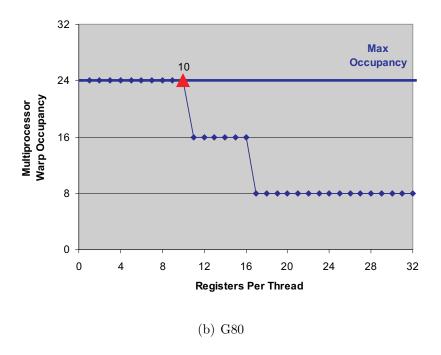

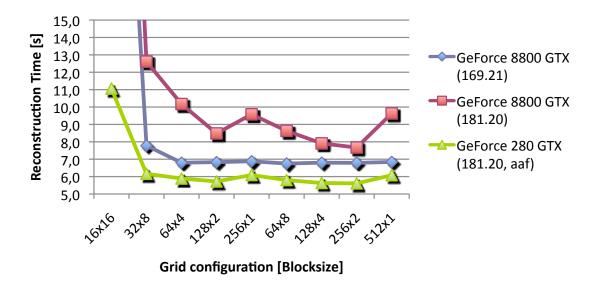

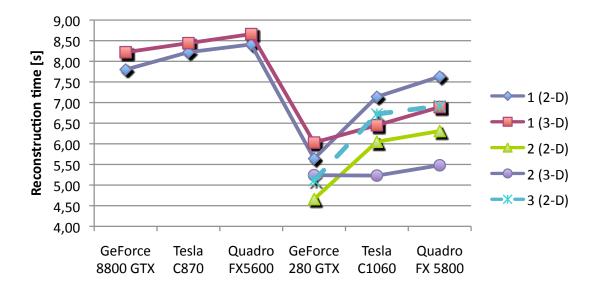

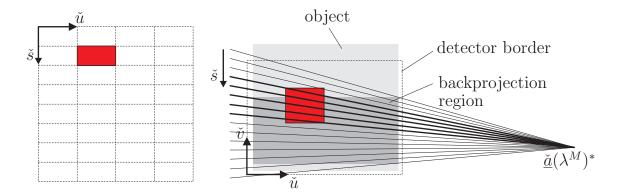

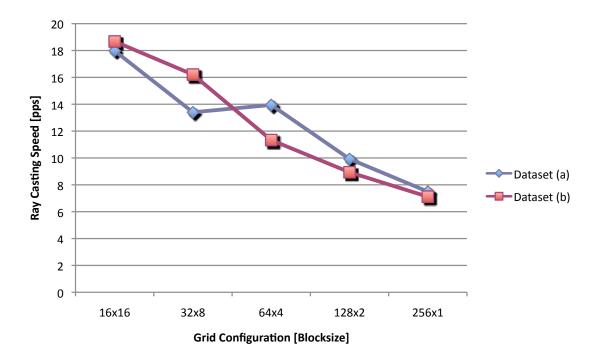

Theoretically exact and stable cone-beam reconstruction algorithms (e.g., the M-line method [Pack 05]) provide excellent image quality without any cone artifacts. Although the M-line approach is still of a filtered back-projection style, it has an increased computational complexity as it requires additional computations for the filtering of the projection images; e.g., derivative computation and filtering along oblique lines in the projection. Thus, especially the filtering of projections incurs much more computations to be performed by the image reconstruction hardware.